Исследование триггеров

Лабораторная работа выполняется с помощью учебного лабораторного стенда LESO2.

1 Цель работы

Целью работы является экспериментальное исследование работы различных типов триггеров.

2 Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

2.1 RS-триггер

- R — установка 0 (от слова reset);

- S — установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q — прямой;

- Q — обратный (инверсный).

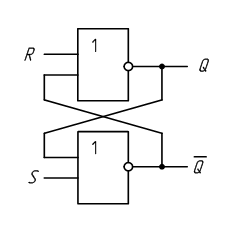

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью (рисунок 2.1).

Рисунок 2.1 — Схема простейшего RS- триггера

Рассмотрим работу триггера:

- Q(t) — состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) — состояние триггера после изменения на входах R и S.

Таблица 2.1 — Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах «И-НЕ» (рисунок 2.2).

Рисунок 2.2 — Схема RS-триггера, построенного на схемах «2И-НЕ»

Входы R и S инверсные (активный уровень «0»). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов «0». Комбинация R=S=0 является запрещённой.

Таблица 2.2 — Таблица переходов RS триггера в базисе «2И-НЕ»

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R = S =0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R =0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S =0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R = S =1 | ||

| 1 | 1 | 1 | 1 |

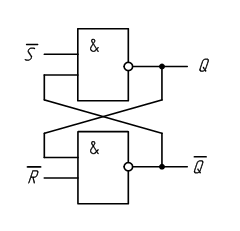

2.2 Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется «опасные гонки»), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена на рисунке 2.3.

Рисунок 2.3 — Схема синхронного RS-триггера

Таблица 2.3 — Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | |||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

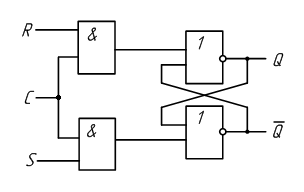

2.3 D — триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Рисунок 2.4 — Схема D-триггера на основе синхронного RS-триггера

Таблица 2.4 — Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| * | Режим хранения информации | |||

| * | 1 | 1 | ||

| 1 | * | Режим записи информации | ||

| 1 | 1 | * | 1 |

2.4 Счётный триггер (Т-триггер)

Т-триггер имеет один счётный информационный вход.Триггер переключается каждый раз в противоположное состояние, когда на вход Т поступает управляющий сигнал.

Таблица 2.5 — Таблица переходов Т триггера

| T | Q(t) | Q(t+1) |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

2.5 Универсальный триггер (JK-триггер)

Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RS-триггера:

- при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1;

- при J= 0, К=1 — переключается в состояние Q=0;

- при J=K=0 — хранит ранее принятую информацию.

Но в отличие от синхронного RS-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещённой комбинацией и приводит триггер в противоположное состояние.

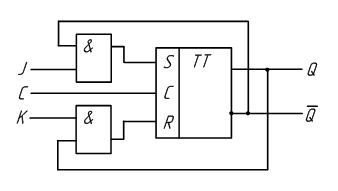

Рисунок 2.6 — Схема JK-триггера на основе двухступенчатого синхронного RS-триггера.

Таблица 2.6 — Таблица переходов JK триггера

| K | J | C | Q(t) | Q(t+1) |

| 1 | ||||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 |

3 Задание к работе

3.1 Исследовать асинхронный RS- триггер

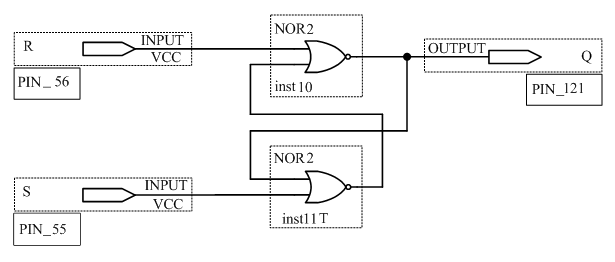

Сконфигурировать ПЛИС в соответствии с рисунком 3.1.

Рисунок 3.1 — RS-триггер на основе логических элементов «ИЛИ-НЕ»

Все используемые элементы располагаются в Symbol tools->Primitives.

Устанавливая с помощью переключателей S7 и S8 различные комбинации логических уровней и наблюдая за светодиодом LED8 заполнить таблицу 3.1

Таблица 3.1 — Таблица переходов для асинхронного RS триггера на элементах «ИЛИ-НЕ»

| R | S | Q(t) | Q(t+1) |

| 1 | |||

| 1 | |||

| 1 | 1 | ||

| 1 | |||

| 1 | 1 |

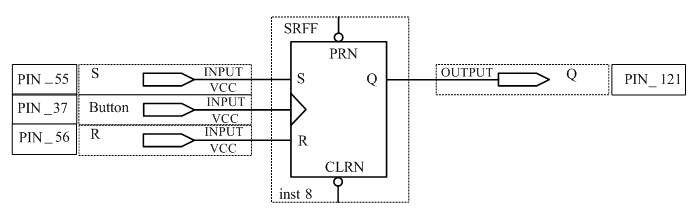

3.2 Исследовать синхронный RS триггер

Сконфигурировать ПЛИС в соответствии с рисунком 3.2.

Рисунок 3.2 — Синхронный RS-триггер

Триггер взять из библиотеки Primitives->Storage. Устанавливая с помощью переключателей S7 и S8 различные комбинации логических уровней и затем нажимая на кнопку Button, заполнить таблицу переходов 3.2.

Таблица 3.2 — Таблица переходов для синхронного RS триггера

| R | S | C | Q(t) | Q(t+1) |

| 1 | ||||

| 1 | 1 | |||

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | ||||

| 1 | ||||

| 1 | 1 | |||

| 1 | ||||

| 1 | 1 |

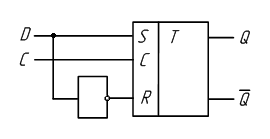

3.3 Исследовать D-триггер

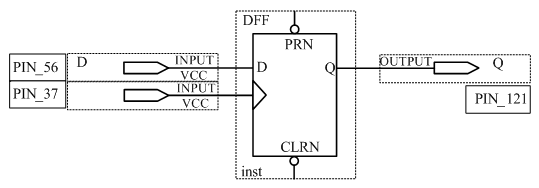

Сконфигурировать ПЛИС в соответствии с рисунком 3.3.

Рисунок 3.3 — Схема D-триггера

Устанавливая с помощью переключателя S8 различные логические уровни на выходе D и затем нажимая на кнопку Button, заполнить таблицу переходов 3.3.

Таблица 3.3 — Таблица переходов для синхронного D триггера

| D | C | Q(t) | Q(t+1) |

| * | |||

| * | 1 | ||

| 1 | |||

| 1 | 1 | 1 |

3.4 Исследовать синхронный T-триггер

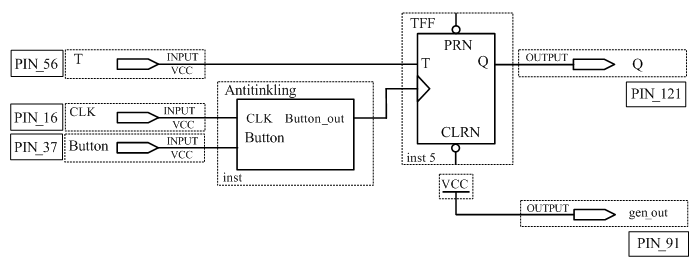

Сконфигурировать ПЛИС в соответствии с рисунком 3.4.

Рисунок 3.4 — Схема счётного Т-триггера

Блок Antitinkling необходим для подавления дребезга кнопки.

ВНИМАНИЕ! Для того, что бы выполнить блок Antitinkling, прочтите инструкцию Борьба с дребезгом контактов.

Вход CLK соединяется с pin16, вход Button соединяется с pin37. Выход Antitinkling соединить с входом синхронизации триггера. Остальные входы соединить согласно рисунку 3.4.

Устанавливая с помощью переключателя S8 различные логические уровни на выходе D и затем, нажимая на кнопку Button, заполнить таблицу переходов 3.4.

Таблица 3.4 — Таблица переходов для синхронного D триггера

| T | C | Q(t) | Q(t+1) |

| 1 | 1 | ||

| 1 | 1 | 1 | |

| 1 | |||

| 1 | 1 |

3.5 Исследование синхронного JK триггера

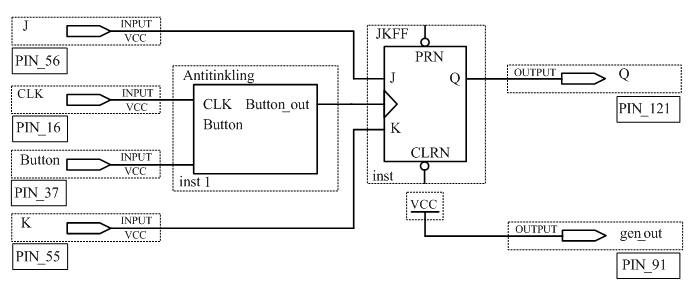

Сконфигурировать ПЛИС в соответствии с рисунком 3.5.

Рисунок 3.5 — Схема JK-триггера

Блок Antitinking подключить так же как, было сделано в предыдущем задании. Устанавливая с помощью переключателя S7 и S8 различные логические уровни на входах J, K и затем, нажимая на кнопку Button, заполнить таблицу переходов 3.5.

Универсальный JK–триггер

Универсальный JK–триггер, схема которого приведена на рис. 8.5.1а, представляет собой двухступенчатый синхронный триггер. Как видно из рисунка, JK-триггер состоит из двух ассинхронных RS-триггеров с инверсными входами и двух КЦУ, каждое из которых содержит две схемы И-НЕ с тремя входами каждая.

а)

б)

Рис. 8.5.1. Структурная схема и обозначение JK-триггера.

Закон функционирования JK-триггера задается табл. 8.5. JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных сигналов на входах J и K. Кроме того, при J=1 и К=1 триггер изменяет свое состояние на противоположное, т.е. работает как триггер со счетным входом (Т-триггер).

Таблица 8.5. Закон функционирования JK-триггера

| C t | ||||||||

| J t | ||||||||

| K t | ||||||||

| Q t | Q t | Q t | Q t | Q t | Q t | Q t | Q t | Q t |

| Q t +1 | Q t | Q t | Q t | Q t | Q t |

При С=0 входы J и К заблокированы и, следовательно, оказываются заблокированными входы S и R ведущего триггера 1. При С=1 в соответствии с информационными сигналами на входах J и К устанавливается состояние ведущего триггера. При этом на входы S и R ведомого триггера 2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С=0, входы триггера 1 закрыты для входной информации, входы триггера 2 открываются и состояние ведущего триггера воспринимается ведомым триггером. Графическое изображение JK-триггера представлено на рис. 8.5.1б.

Одним из широко используемых вариантов построения является схема JK-триггера с входной логикой (рис. 8.5.2а). Условное обозначение триггера дано на рис. 8.5.2б. При С=1 вторая ступень блокирована, а информационные сигналы устанавливают состояние первой ступени. При сигнале С=0 вторая ступень воспринимает состояние первой. Требуемое начальное состояние триггера устанавливается с помощью сигналов, подаваемых на входы RS-триггеров первой и второй ступени. В схеме триггера имеется по три конъюктивно связанных входа J и К. Другими словами, в структурную схему триггера встроены логические элементы. Их можно использовать для построения сложных схем.

а)

б)

Рис. 8.5.2. Структурная схема и обозначение JK-триггера с входной логикой

Т-триггеры

Т-триггеры, или триггеры со счетным входом, могут быть получены из JK-триггера при соединении обоих информационных входов J и К и подаче на них уровня 1 (рис. 8.6.1.).

Рис. 8.6.1. Обозначение Т-триггера

Функционирование Т-триггера описывается в табл. 8.6. В качестве счетного входа Т используется вход С. При подаче сигнала на вход Т-триггер будет переключаться в состояние, противоположное предыдущему.

Таблица 8.6. Закон функционирования Т-триггера

| C t | J t | K t | Q t | Q t +1 |

| Q t | Q t | |||

| Q t |

JK-триггер в таком режиме выполняет функцию Т-триггера. Следует заметить, что уровень для входов J и К (входов элементов И-НЕ) является пассивным сигналом. Поэтому для получения Т-триггера из JK триггера можно не предусматривать входы J и К в схеме (рис. 8.6.2а). Разновидностью Т-триггера является ТV-триггер, в котором вход V является управляющим. При V=1 TV-триггер превращается в Т-триггер. При V=0 TV-триггер сохраняет свое состояние неизменным (рис. 8.6.2б).

Рис. 8.6.2. Варианты реализации Т-триггера

D-триггер

D-триггер, или триггер задержки, имеет один информационный вход (D-вход) и вход для синхронизации С. Основное назначение D-триггера — задержка сигнала, поданного на вход D. D-триггер может быть получен из JK-триггера соединением входа J с входом К через инвертор НЕ. Полученный таким образом вход будет называться D-входом. Схема D-триггера представлена на рис. 8.7.1а. Условное обозначение D-триггера приведено на рис. 8.7.1б.

Рис. 8.7.1. Структурная схема и обозначение D-триггера

Функционирование D-триггера описывается табл. 8.7. Под действием синхросигнала С информация, поступающая на вход D, принимается в триггер, но на выходе Q появляется с задержкой на один такт.

Таблица 8.7. Закон функционирования D-триггера

| C t | J t | K t | Q t | Q t +1 |

| Q t | Q t | |||

| Q t | Q t | |||

| Q t | ||||

| Q t |

Контрольные вопросы

1. Какое устройство называется последовательностным? Опишите его структуру.

2. Проведите классификацию триггеров.

3. Каковы основные характеристики триггеров?

4. Опишите работу RS-триггера с прямыми входами с помощью структурной схемы, таблицы истинности.

5. Опишите работу RS-триггера со статическим управлением с помощью структурной схемы, таблицы истинности.

6. Опишите работу универсального JK-триггера по структурной схеме и таблице истинности.

7. Опишите работу Т-триггера по структурной схеме и таблице истинности.

8. Опишите работу D-триггера по структурной схеме и таблице истинности.

Типовые ПЦУ

Регистры

Регистром называется последовательностное цифровое устройство, используемое для хранения и выполнения логических преобразований над n-разрядным двоичным числом. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано некоторое КЦУ, с помощью которого обеспечивается выполнение логических операций или микроопераций над n-разрядными словами в ПЦУ. В регистре могут выполняться следующие микрооперации: прием слова из другого ПЦУ, передача слова из регистра в другое ПЦУ, поразрядные логические операции, сдвиг слова влево или вправо на заданное число разрядов, преобразование последовательного кода слова в параллельный и обратно, установка регистра в начальное состояние (сброс). Схемы выполнения микроопераций реализуется с помощью КЦУ.

Схема регистра для хранения n-разрядного двоичного слова приведена на рис. 9.1.1а. Регистр S состоит из n триггеров. Состояние регистра определяется состоянием триггеров. Оно представляется набором выходных сигналов в парафазном коде . На регистр S может быть подано для хранения двоичное n-разрядное слово X=<<i>xn, xn—1, . x1> с помощью совокупности входных сигналов в парафазном коде .

Если на входы поступают сигналы Xi, равные 0 или 1, то триггеры регистра S устанавливаются в состояния в соответствии со значениями переменных Xi. Триггеры регистра сохраняют значение S=X до прихода новых входных сигналов. В регистре S(n) каждый i-ый элемент (триггер) соответствует двоичной переменной Si и является i-ым разрядом регистра S. Число разрядов в регистре определяет его длину.

Используемое для регистров условное обозначение дано на рис. 9.1.1б. Указываются наименование регистра (S), старший (n) и младший (1) разряды.

Состояние регистра представляется целым числом в двоичной системе счисления. Для сокращения записи состояния регистра можно использовать восьмеричную и шестнадцатеричную формы представления двоичных чисел. Состояние регистра можно представить не только в двоичном алфавите, но и в любом другом.

Рис. 9.1.1. Структурная схема регистра и его обозначение

Регистры играют важную роль при построении сложных цифровых устройств. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом с помощью соответствующих схем КЦУ рис. 9.1.2.

Рис. 9.1.2. Структурная схема цифрового устройства, использующего регистры и КЦУ

Анализ схемы регистра позволяет отметить характерную особенность — однородность (регулярность) структуры.

Регистр состоит из однотипных элементов (триггеров), которые регулярно размещены друг относительно друга. Однородность элементов с регулярным размещением их в регистре позволяет существенно упростить процессы изготовления, контроля, эксплуатации. Упрощается так же описание и изучение регистра. Регистр можно описать совокупностью однотипных автоматов. Достаточно задать автоматное описание для одного элемента регистра и указать число элементов. Регулярность схемы регистра позволяет прийти к выводу о возможности построения регулярных схем КЦУ для выполнения микроопераций на множестве однотипных элементов. Это дает возможность довольно просто осуществлять синтез схемы КЦУ, сводя его к синтезу многократно повторяющейся схемы КЦУ для одного разряда регистра и схемы, обеспечивающей взаимодействие (при необходимости) двух соседних разрядов. Такой подход позволяет свести сложное описание КЦУ в виде совокупности булевых функций от переменных к простому описанию КЦУ. При этом КЦУ можно представить в виде повторяющегося n раз набора булевых функций от конечного числа m переменных, где mn.

В зависимости от типа выполняемых в регистре микроопераций различаются следующие типы регистров:

· с параллельным приемом и выдачей информации;

· с последовательным приемом и выдачей информации;

· с последовательным приемом и параллельной выдачей информации;

· с параллельным приемом и последовательной выдачей информации.

В зависимости от числа входных и выходных каналов регистры делятся на однофазные (сигналы передаются по одному каналу) и парафазные (передача сигналов по двум каналам). Парафазные регистры реализуются на RS-триггерах, а однофазные — на D-триггерах. Регистры характеризуются числом разрядов и быстродействием, определяемым максимальной тактовой частотой приема, передачи и сдвига информации.

Регистры памяти

Регистр с параллельным приемом и выдачей информации называется регистром памяти. В качестве элементов регистра памяти используются синхронные D-триггеры при однофазных входных сигналах (рис. 9.1.3.) или RS-триггеры при парафазных входных сигналах (рис. 9.1.4.).

Предварительная установка регистра в нулевое состояние осуществляется посылкой “Установить 0” на асинхронные входы сброса триггеров. Изменение информации в регистре происходит после изменения сигналов на входах X при поступлении сигнала на вход синхронизации С.

Рис. 9.1.3. Регистр памяти на Рис. 9.1.4. Регистр памяти на

Регистры сдвига

Регистры с последовательным приемом или выдачей информации получили название регистров сдвига.

В регистре сдвига вправо первый разряд вводимого числа X1 подается на вход одного, крайнего слева, разряда Sn регистра и вводится в него при поступлении первого сигнала синхронизации С. С приходом следующего сигнала синхронизации значение X1 c выхода разряда Sn вводится в разряд Sn-1, а в разряд Sn поступает X2. В каждом такте производится сдвиг поступающей информации на один разряд вправо. После n сдвигов синхронизации весь регистр оказывается заполненным разрядами числа X, и первый разряд числа X1 появится на выходе S1. Если подать последовательность из n сигналов синхронизации и на вход разряда Sn подать X=0, то из регистра будет выводиться число X через выход S1 и в конце вывода регистр будет освобожден от хранения числа X. Регистры сдвига реализуются на D-триггерах (рис. 9.1.5.) или RS-триггерах (рис. 9.1.6.). В последней схеме для ввода информации в первый разряд включается схема инвертора.

Рис. 9.1.5. Структурная схема регистра сдвига на D-триггерах

Рис. 9.1.6. Структурная схема регистра сдвига на RS-триггерах

Для параллельного вывода информации из регистра сдвига необходимо все выходы разрядов регистра сдвига подключить к различным полюсам Sn, Sn-1, . S1. Для реализации регистров сдвига применяются так же триггеры с динамическим управлением по входу С. Применение таких триггеров гарантирует нормальную работу регистра сдвига. Схема регистра сдвига влево на D-триггерах с динамическим управлением представлена на рис. 9.1.7.

Рис. 9.1.7. Структурная схема регистра сдвига влево

Комбинируя схемы сдвига вправо и влево и используя управляющие сигналы, можно построить регистр сдвига в обоих направлениях. Такой регистр называется реверсивными (рис. 9.1.8.). При подаче разрешающего сигнала на управляющий вход V1 включается схема сдвига вправо. Реверсивный регистр при этом превращается в регистр сдвига вправо. При подаче разрешающего сигнала на управляющий вход V2 включается схема сдвига влево. Реверсивный регистр превращается в регистр сдвига влево.

Рис. 9.1.8. Структурная схема реверсивного регистра

В регистрах сдвига влево и вправо разряды двоичного кода выходят за пределы разрядного регистра. Если соединить выход крайнего правого разряда регистра со входом крайнего левого разряда, то получим схему кольцевого (циклического) регистра сдвига. Реверсивные регистры можно использовать для построения стековых регистров, имеющих единственный общий вход и выход. Такие регистры работают по принципу “первый вошел – последний вышел”. Стековые регистры называются так же регистрами магазинного типа.

Возможно так же совмещение в одной схеме регистра памяти и регистра сдвига. На рис. 9.1.9. представлена схема, выполняющая функции 4-разрядного регистра памяти и 4-разрядного регистра сдвига влево. В каждом разряде регистра использован D-триггер с двумя D-входами и двумя управляющими V-входами. При подаче V1=0 D-входы, используемые в схеме сдвига, отключаются и схема превращается в схему регистра памяти с однофазными входами и парафазными выходами. При подаче V2=1 разрешается прием информации, которая поступает на входы в параллельной форме и при подаче разрешения на вход синхронизации С передается в регистр. Если подается V1=1, то схема превращается в схему регистра сдвига влево. В такой схеме прием информации осуществляется параллельно, а выдача либо последовательно либо параллельно.

Рис. 9.1.9. Схема, совмещающая регистр памяти и регистр сдвига влево

На рис. 9.1.10. показано условное графическое изображение схемы регистра памяти и сдвига. Стрелка, стоящая рядом с символом регистра RG, указывает направление сдвига.

Рис. 9.1.10. Графическое обозначение регистра памяти и сдвига

Применениерегистров

Регистры находят применение при выполнении различных временных преобразований информации. Регистры сдвига используются в схемах умножения и деления: сдвиг числа влево и вправо на один разряд соответствует его умножению или делению на два. Регистры можно использовать для задержки передаваемой информации на n тактов. В сложных ПЦУ, состоящих из большого числа регистров, возникает необходимость передачи слов с одного регистра на другой. Это можно осуществить с помощью специальной микрооперации передачи слова. Два регистра соединяются друг с другом с помощью КЦУ, реализующего управляемую схему передачи. Передачу слова из регистра S в регистр R можно записать в виде микрооперации передачи R:=S.

Cчетчики

Основные понятия

Последовательностное цифровое устройство, обеспечивающее хранение информации и выполнение над ним микрооперации счета, называется счетчиком.

Микрооперация счета заключается в изменении значении числа С в счетчике на 1. Счетчик, в котором выполняется микрооперация счета С:=С+1, называется суммирующим, а счетчик, реализующий микрооперацию С:=С-1, — вычитающим. Счетчик называется реверсивным, если реализуются обе микрооперации.

Основным параметром счетчика является модуль счета КС, определяемый максимальным числом единичных сигналов, которое может быть сосчитано счетчиком. Счетчик, содержащий n двоичных разрядов, может находиться в состояниях 0, 1, 2, …., 2 n -1. При поступлении на вход суммирующего счетчика 2 n -й единицы он переходит из состояния 2 n -1 в состояние 0. Таким образом, n-разрядный суммирующий двоичный счетчик имеет модуль счета КС=2 n .

Счетчики характеризуются так же быстродействием, которое определяется допустимой частотой входных сигналов и временем установки состояния счетчика.

Счетчики обычно реализуются на Т-триггерах. Однако для их построения могут применяться не только триггеры со счетным входом, но и D-триггеры, JK-триггеры.

Счетчики можно классифицировать по нескольким признакам. В зависимости от направления счета различают суммирующие (с прямым счетом), вычитающие (с обратным счетом) и реверсивные (с прямым и обратным счетом). По способу организации схемы переноса различаются счетчики с последовательным и параллельно-последовательным переносом. В зависимости от наличия синхронизации различают синхронные и асинхронные счетчики.

При маркировке для обозначения счетчика используются буквы ИЕ. Конструктивно счетчики выполняются в виде совокупности интегральных схем — триггеров, соединенных соответствующим образом или в виде одной интегральной схемы, содержащей многоразрядный счетчик.

Суммирующие двоичные счетчики

В суммирующем двоичном n-разрядном счетчике, состоящем из триггеров, реализуется счетная последовательность чисел. Эта последовательность начинается с 0. Очередное число в этой последовательности получается прибавлением единицы к предыдущему числу. После того как последовательность доходит до максимального числа 2 n -1, она снова проходит через 0 и повторяется. В счетчике с n триггерами число возможных состояний равно 2 n , модуль счета КC так же равен 2 n . Каждому состоянию счетчика соответствует число в счетной последовательности от 0 до 2 n -1.Рассмотрим устройство двоичного 3-разрядного суммирующего счетчика. В таком счетчике можно реализовать счетную последовательность от 0 до 2 3 -1=7. Последовательность чисел может быть задана совокупностью 3-разрядных двоичных чисел b3b2b1: 000, 001, 010, 011, 100, 101, 110, 111. Поставим в соответствие каждому разряду bi числа выход триггера Qi. В 3-разрядном счетчике с выходами Q3Q2Q1 будет реализовываться счетная последовательность от 0 до 7.

Счетчик может быть реализован с использованием двухступенчатых триггеров Т со счетным входом. Схема двоичного 3-разрядного суммирующего счетчика представлена на рис.9.2.1. В этой схеме исходное состояние счетчика устанавливается подачей сигнала по шине “Уст.0.” Триггеры Т изменяют свое состояние с окончанием входного сигнала, т.е. после перехода от уровня 1 к 0. Входной сигнал по шине С подается на счетный вход триггера 1. Работа счетчика может быть описана с помощью временной диаграммы (рис. 9.2.1).

Рис. 9.2.1. Структурная схема и временные диаграммы суммирующего счетчика

Закон функционирования счетчика можно представить в виде табл. 9.1., условное изображение счетчика приведено на рис. 9.2.2.

Таблица 9.1. Закон функционирования суммирующего счетчика

| Номер комби-нации | Состояния триггеров | ||||

| Q t 3 | Q t 2 | Q t 1 | Q t +1 3 | Q t +1 2 | Q t +1 1 |

Рис. 9.2.2. Графическое обозначение двоичного счетчика

Работу счетчика можно так же представить как процесс суммирования предыдущего значения счетчика с единицей. Такое суммирование выполняется по обычным правилам выполнения операции сложения чисел в двоичной системе.

Вычитающие и реверсивные двоичные счетчики

В вычитающих счетчиках с приходом очередного счетного сигнала предыдущий результат уменьшается на единицу. В вычитающем двоичном n-разрядном счетчике реализуется счетная последовательность чисел, начиная с 2 n -1 и кончая 0. Очередное число в этой последовательности получается вычитанием единицы из предыдущего числа. После получения значения 0 последовательность повторяется. Порядок смены состояний вычитающего счетчика может быть описан табл. 9.2.

Таблица 9.2. Порядок смены состояний вычитающего счетчика

| Номер комби-нации | Состояния триггеров | ||||

| Q t 3 | Q t 2 | Q t 1 | Q t +1 3 | Q t +1 2 | Q t +1 1 |

Из таблицы следует еще одно отличие вычитающего счетчика от суммирующего: триггер каждого предыдущего разряда переходит в другое состояние при сигнале займа, обратном сигналу переноса в суммирующем счетчике. Поэтому вычитающий счетчик в отличие от суммирующего строится так, что со входом каждого последующего триггера соединяется инверсный выход предыдущего триггера. Схема вычитающего счетчика с последовательной передачей переносов приведена на рис. 9.2.3.

Рис. 9.2.3. Структурная схема вычитающего счетчика с последовательным переносом

Функционирование i-ого разряда вычитающего счетчика можно описать логическими выражениями переноса Пi+1 разности Сiпо табл. 9.3.

Таблица 9.3. Функционирование i-ого разряда вычитающего счетчика

| bi | Пi | Ci | Пi+1 |

Таблица получается на основании анализа особенностей вычитания единицы из двоичного числа. Из табл. 9.3. следуют логические выражения:

Разность Сi определяется тем же выражением, что и в суммирующем счетчике, поэтому перенос должен подаваться на счетный вход триггера Т. В отличие от суммирующего счетчика в выражении для Пi+1 вместо biиспользуется . Следовательно, на элементы И, формирующие переносы, подаются сигналы с инверсионных выходов триггера. Для ускорения работы вычитающих двоичных счетчиков могут использоваться схемы с параллельным и с параллельно-последовательным переносом.

В реверсивном счетчике объединяются схемы суммирующего и вычитающего счетчиков. Кроме того, существует возможность управления направлением счетчика, для чего предусматривается дополнительное КЦУ.

В реверсивном счетчике на Т-триггерах (рис. 9.2.4а) счетные сигналы поступают на вход Т-триггера через логические элементы, если они открыты единичными сигналами с выходов предыдущих разрядов.

Для счетных сигналов предусмотрены два входа. Если счетчик работает как суммирующий, сигналы счета следует подавать на вход «+1». Для вычитающего счетчика сигналы счета подаются на вход «-1». На выходе счетчика, обозначенном «15», сигнал появляется при переходе счетчика в состояние с номером 15, в котором все триггеры установлены в состояние 1. На этом выходе формируется сигнал переноса в следующий счетчик. На выходе «0» сигнал появляется при заполнении счетчика нулями. Это сигнал займа в следующий счетчик в схеме вычитающего счетчика. Условное обозначение реверсивного счетчика с двумя входами приведено на рис. 9.2.4б.

Рис. 9.2.4. Структурная схема реверсивного счетчика и его графическое обозначение

Синхронные и асинхронные двоичные счетчики

Двоичные счетчики, состояние триггеров которых изменяется одновременно под воздействием сигнала синхронизации на входах всех триггеров, получили название синхронных. Схема синхронного счетчика со сквозным переносом на Т-триггерах приведена на рис. 9.2.5а., его условное обозначение дано на рис. 9.2.5б.

а)

б)

Рис. 9.2.5. Структурная схема счетчика со сквозным переносом и его обозначение

Синхронные счетчики используются в синхронных цифровых системах. Последовательностные цифровые устройства в этих системах обычно зависят друг от друга и управляются от общего источника синхросигналов. В таких условиях нужно, чтобы все триггеры во всех ПЦУ изменяли свое состояние одновременно по сигналу синхронизации, чтобы текущее состояние триггеров использовалось для определения их следующего состояния. Применяемая здесь схема со сквозным переносом легко наращивается простым добавлением схемы И с двумя входами. Однако для определения значения самого правого входа Т n-разрядного счетчика необходимо время, равное времени распространения сигнала через одну схему И, умноженному на n-1.

Что такое триггер в электронике — подробно разбираемся в терминах

Существует несколько различных типов триггеров, из которых JK считается наиболее универсальным. JK-триггеры находят применение и как отдельные микросхемы, и в качестве элементов для процессоров. Их использование позволяет создавать схемы, действующие по достаточно сложным алгоритмам.

Что такое тригеры —кратко

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Он имеет два симметричных входа S и R и два симметричных выхода Q и , причем выходной сигнал Q является логическим отрицанием сигнала . На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ( ). Наличие импульса на входе будем считать единицей, а его отсутствие — нулем. На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

| S | R | Q |

| запрещено | ||

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 | хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

- Если на входы триггера подать S=”1″, R=”0″, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=”0″, Q=”0″ и выход станет равным “1”.

- Точно так же при подаче “0” на вход S и “1” на вход R на выходе появится “0”, а на Q — “1”.

- Если на входы R и S подана логическая “1”, то состояние Q и не меняется.

- Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Таблица истинности

Работу триггера РС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно➡ Что такое короткое замыкание

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Классификация последовательных схем

Последовательные схемы могут быть использованы для простых триггеров или для создания более сложных систем: устройств памяти, счетчиков, регистров сдвига. Они подразделяются на три основные категории:

- Асинхронные, меняющие статус при включении;

- Синхронные, согласованные с тактовым сигналом;

- Комбинированные, реагирующие на запуск импульсов.

Важно! Если схема зависит от внешнего входа, то она является асинхронной. Если состояния меняются в зависимости от тактового сигнала, то она синхронная. Для сохранения состояния присутствует обратная связь, когда частично сигнал с выхода идет опять на вход.

D – триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| * | Режим хранения информации | |||

| * | 1 | 1 | ||

| 1 | * | Режим записи информации | ||

| 1 | 1 | * | 1 |

Если на входе D – “1”, то по приходу синхроимпульса Q = 1. Если на D “0”, то Q =0.

Алгоритм работы

Если на вход C поступает сигнал, равный нулю, то выходные значения будут сохранены. Как только он станет равным единице, формирование значения Q будет происходить по следующим правилам:

- Если J=K=0, режим триггера не меняется.

- Когда J и K равны 1, происходит изменение состояния элемента на противоположное при поступлении каждого тактового импульса. В этом случае триггер функционирует идентично делителю частоты. Такой режим работы называют счётным, поскольку его использование позволяет осуществлять подсчёт определённых событий.

- При K = 1, J = 0 выходное значение принимает нулевое значение.

- Если K = 0, J = 1, тогда на выходе будет получена единица.

Алгоритм работы отображает таблица истинности JK-триггера, так как каждой входной комбинации значений соответствует строго определённая выходная.

Разобраться в работе триггера помогает еще временная диаграмма, на которой графически отображаются сигнальные импульсы, присутствующие одновременно на входах и выходах устройства.

На приведённой диаграмме срабатывание происходит по фронту импульса C с задержкой. Момент, когда это происходит, зависит от конкретной схемы реализации.

Универсальный триггер (JK-триггер)

Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RS-триггера:

- при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1;

- при J= 0, К=1 – переключается в состояние Q=0;

- при J=K=0 – хранит ранее принятую информацию.

Но в отличие от синхронного RS-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещённой комбинацией и приводит триггер в противоположное состояние.

Таблица переходов JK триггера

| K | J | C | Q(t) | Q(t+1) |

| 1 | ||||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 |

Цифровая электроника – ЯБ-триггеры с доминирующим Я-входом

Наличие запрещенных комбинаций для тактируемых &У-триггеров вызвало идею построения триггера, который принудительно устанавливает Qx в 0 при S= 1 и R = 1, при подаче синхроимпульса. Это становится возможным благодаря особенному подключению входов. На рис. 7.35 показано такое соединение входов. При S = 1 и R = 1, 1-сигнал не может воздействовать на триггер, так как на выходе элемента НЕ действует 0. И-элемент запирается. 1-сигнал на R разрешает сброс. Режим установки при S = 1 и R = 0 остается возможен, так как теперь на выходе элемента НЕ действует 1 и И-элемент имеет на выходе 1.

Интересная статья: Что такое твердотельное реле?

Такой триггер называется .RS’-триггером с доминирующим /?-входом, или ^триггером. Правило его работы следует из условного обозначения на рис. 7.36 (см. также разд. 7.1). Оно гласит: если оба входа триггера S, R и вход Т имеют уровень 1, то при сигнале синхронизации 1 Q< устанавливается на 0, a Q2 — на 1. Таблица истинности тактируемого ЛУ-триггера с доминирующим R-входом представлена на рис. 7.37. Разумеется, существует также тактируемый RS-триггер с доминирующим ^-входом (см. контрольный тест).

Будет интересно➡ Что такое анод и катод, в чем их практическое применение

Временные диаграммы

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Цифровая электроника

Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколько угодно долго. В общем случае триггер имеет два выхода: прямой и инверсный. Состояние триггера принято определять по значению потенциала на прямом выходе. Если на прямом выходе имеется потенциал равный логической единице, то триггер находится в единичном состоянии (при этом потенциал инверсного выхода равен логическому нулю). В противном случае триггер находится в нулевом состоянии. В основу классификации потенциальных триггеров, в которых имеется связь по постоянному току между входами и выходами, положены два основных признака: функциональный и способ записи информации в триггер.

Функциональная классификация является наиболее общей и представляет собой классификацию триггеров по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания t n и после t n +1 . В соответствии с функциональной классификацией различают RS-, D-, T- и JK-триггеры.

Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е. определяет ход процесса записи информации в триггер. По этой классификации триггеры подразделяются на асинхронные и тактируемые. Отличительной особенностью асинхронных триггеров является то, что запись информации в них осуществляется статическим способом, т.е. непосредственно с поступлением информационного сигнала на его вход. Запись информации в тактируемый триггер, имеющий информационные и тактовые входы, осуществляется только при подаче разрешающего или тактирующего импульса. Среди тактируемых триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала или, что одно и то же, по его переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (по заднему фронту). Такое управление тактируемыми триггерами называется динамическим. Кроме того, тактируемые триггеры подразделяются на однотактные и многотактные в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое.

При проектировании устройств с применением триггеров, кроме значения функции, выполняемой триггером, необходимо знать его основные схемотехнические параметры. К таким параметрам относятся как стандартные параметры любой логической микросхемы – это нагрузочная способность, коэффициент объединения по входу, время задержки и т.д., так и индивидуальные:

- минимальная длительность входного сигнала — определяет минимально допустимую длительность входного сигнала, при которой еще происходит переключение триггера из одного состояния в другое;

- максимальная частота переключения триггера определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности.

Закон функционирования триггера удобно отображать с помощью так называемых таблиц переходов, в которых даются состояния входов и выходов триггера в момент времени до его срабатывания t n и после t n +1 , при этом выходное состояние может обозначаться следующим образом:

0 — триггер находится в состоянии Q=0;

1 — триггер находится в состоянии Q=1;

Q — состояние триггера не изменяется при изменении информации на входе;

— состояние триггера изменяется на противоположное при изменении информации на входе;

Х — неопределенное состояние триггера — характеризуется тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы ( или ), а после окончания действия информационного сигнала триггер может оказаться в состояние Q=1 или Q=0 с равной вероятностью.

Перейдем к рассмотрению триггеров различных типов.

RS-триггер. Триггером RS-типа называется логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает единичное состояние (Q=1), а при S=0, R=1 — нулевое (Q=0). Вход S называется единичным, а R — нулевым. Принцип работы RS-триггера можно задать таблицей переходов, где Q n – исходное состояние триггера:

Для того, чтобы найти логическое уравнение RS-триггера, преобразуем таблицу переходов к виду, в котором состояние Q n определим конкретными значениями и представим его в виде входной переменной:

Запишем СДНФ для функции Q n +1 (неопределенные состояние не учитываются)

Для минимизации СДНФ заполним диаграмму Вейча, в которой отметим также неопределенные значения функции Q n +1 ( рис. 5.2,а ). Из диаграммы видно, что в результате склейки можно получить две простые импликанты и. Так как функция является частично определенной, то для избавления от переменной в импликанте , можно неопределенные значения в диаграмме заменить единичными значениями и произвести склейку всего одной переменной S n ( рис. 5.2,б ). МДНФ, таким образом примет вид, который и будет соответствовать логическому уравнение RS-триггера

Рис. 5.2. Диаграммы Вейча для асинхронного RS-триггера.

Полученное уравнение задает работу асинхронного RS-триггера. Состояние такого триггера определяется только значениями сигналов R и S. Асинхронный RS-триггер можно построить на логических элементах И-НЕ, ИЛИ-НЕ. Преобразуем логическое уравнение асинхронного RS-триггера, используя законы отрицания алгебры логики:

Для реализации триггера на элементах ИЛИ-НЕ проведем отрицание обеих частей полученного уравнения

Таким образом, сигнал на инвертирующем выходе RS-триггера — это сигнал на выходе элемента ИЛИ-НЕ, на один вход которого подан сигнал S, а на второй — сигнал с выхода другого элемента ИЛИ-НЕ ( рис. 5.3,а ).

Рис. 5.3. Структурные схемы асинхронных RS-триггеров на базе элементов ИЛИ-НЕ, И-НЕ и УГО асинхронного RS-триггера с инверсными входами.

Для реализации RS-триггера на элементах И-НЕ, необходимо выполнить следующие преобразования:

Структурная схема асинхронного RS-триггера, соответствующая полученному уравнению, изображена на рис. 5.3,б , а условное графическое изображение – на рис. 5.3,в . Из рисунка видно, что на вход триггера на элементах И-НЕ сигналы R и S необходимо подавать в инверсном виде.

В качестве самостоятельных устройств асинхронные RS-триггеры находят ограниченное применение, но являются базовыми схемами для более сложных триггерных устройств. В устройствах цифровой обработки находят применение тактируемые RS-триггеры, которые называются еще синхронными. Эти триггеры, кроме входов установки R и S, имеют вход разрешения записи C. Срабатывание синхронного триггера происходит только при наличии активного сигнала на этом входе. Работа синхронного RS-триггера задается таблицей переходов:

Из таблицы видно, что до тех пор, пока сигнал C n имеет значение логического нуля, триггер сохраняет свое состояние неизменным. Как только C n становится равным логической единицы, работа синхронного триггера разрешается, и его состояния соответствуют состояниям асинхронного триггера. Алгоритм нахождения логической функции синхронного RS-триггера аналогичен алгоритму нахождения логической функции асинхронного RS-триггера. Преобразуем таблицу переходов к виду:

Заполним диаграмму Вейча с учетом неопределенных состояний ( рис. 5.4,а ). С целью упрощения МДНФ зададим вместо неопределенных значений единичные и найдем простые импликанты путем склеивания, как это показано на рис. 5.4,б . На рисунке специально не была произведена склейка импликанты с целью соблюдения аналогии ФАЛ асинхронного и синхронного RS-триггеров.

Рис. 5.4. Диаграммы Вейча для синхронного RS-триггера.

Согласно диаграмме запишем минимальную ФАЛ и выполним следующее преобразование

Полученная ФАЛ содержит два слагаемых. Первое слагаемое представляет собой логическою конъюнкцию инверсного значения сигнала тактирования и сигнала состояния триггера до срабатывания, а второе – логическую конъюнкцию прямого значения сигнала тактирования и ФАЛ асинхронного RS-триггера.

Для реализации структурной схемы синхронного RS-триггера необходимо сигналы установки S и R асинхронного триггера стробировать сигналом разрешения C. Сделать это можно, используя логические элементы И, либо И-НЕ. В первом случае стробированные сигналы R и S будут представлены в прямом виде, поэтому их необходимо подавать на схему асинхронного RS-триггера на элементах ИЛИ-НЕ ( рис. 5.5,а ). Во втором случае сигналы R и S окажутся проинвертированными. Поэтому в качестве асинхронного следует выбрать триггер на базе элементов И-НЕ ( рис. 5.5,б ).

Рис. 5.5. Варианты структурных схем синхронных RS-триггеров.

Часто синхронные триггеры любых типов имеют дополнительные входы асинхронной установки в нуль или единицу. Структурная схема такого синхронного RS-триггера приведена на рис. 5.6,а , а его условное графическое обозначение – на рис. 5.6,б .

Рис. 5.6. Структурная схема синхронно RS-триггера с входами асинхронной установки и его условное графическое обозначение.

Поскольку триггер, изображенный на структурной схеме, реализован на элементах И-НЕ, то сигналы асинхронной установки R и S должны иметь инверсные активные уровни. Кроме того, поскольку сигналы асинхронной установки подаются непосредственно на выходной каскад (асинхронный RS-триггер), то они имеют больший приоритет перед остальными сигналами триггера.

D-триггер. D-триггер относится к одновходовым триггерам. Асинхронный D-триггер имеет один вход D и прямой и инверсный выходы Q и . Работа асинхронного D-триггера задается таблицей переходов:

Соответствующее таблице истинности логическое уравнение имеет вид

Логическое уравнение показывает, что состояние D-триггера в момент времени t n +1 соответствует значению сигнала на D-входе в момент времени t n , т.е. с помощью D-триггера осуществляется задержка входного сигнала. Отсюда второе название асинхронного D-триггера – триггер задержки. Асинхронный D-триггер не имеет практического применения, поскольку его функцию может выполнять схема из последовательного соединения двух инверторов. Наибольший интерес представляет тактируемый (синхронный) D-триггер, работа которого описывается таблицей переходов:

Аналогично, как и в случае с RS-триггером, можно составить логическое уравнение синхронного D-триггера, соответствующее приведенной таблице переходов:

Из уравнения видно, что при наличии тактирующего сигнала (С=1), триггер переходит в состояние Q n +1 =D n ,а при отсутствии тактирующего сигнала (С=0), триггер сохраняет предыдущее состояние Q n +1 =Q n . Иными словами, синхронный D-триггер осуществляет запись информационного разряда по активному уровню сигнала C с последующим его хранением. Отсюда синхронный D-триггер имеет другое название – триггер-защелка.

Рассмотрим вариант реализации синхронного D-триггера на элементах И-НЕ. Для этого выполним следующие преобразования над задающей его работу ФАЛ

Полученное уравнение совпадает по своей структуре с уравнением для асинхронного RS-триггера, при условии, что , . Тогда очевидно, что D-триггер представляет собой RS-триггер, на информационные входы которого поданы сигналы в соответствии с полученными выражениями. Поскольку сигналы R и S на вход RS-триггера на базе элементов И-НЕ должны подаваться в инверсном виде, то для получения D-триггера, на входы RS-триггера необходимо подавать . Преобразуем выражение для к виду:

С учетом полученных выражений, структурная схема синхронного D-триггера на базе элементов И-НЕ может быть представлена совокупностью двух каскадов. Первый выполняет функцию формирования сигналов и , а второй – асинхронного RS-триггера ( рис. 5.7,а ). На рис. 5.7,б показано условное графическое обозначение D-триггера.

Рис. 5.7. Структурная схема синхронного D-триггера на элементах И-НЕ и его УГО.

Т-триггер. Триггер T-типа является одновходовым устройством с двумя устойчивыми состояниями, изменяющимися каждый раз на противоположные при подаче на вход Т управляющего сигнала. Работа Т-триггера задается таблицей переходов:

Составленное по таблице переходов СДНФ для Q n +1 уже имеет минимальный вид

Характерной его особенностью является то, что частота изменения потенциала на его выходах в два раза меньше частоты сигналов на входе T ( рис. 5.8 ). Это свойство используется при построении двоичных счетчиков. Отсюда второе название T-триггера – счетный триггер.

Рис. 5.8. Диаграммы входного и выходного потенциалов T-триггера.

Структуру T-триггера можно определить путем преобразования его логической функции к удобному для синтеза в заданном базисе виду. Однако, из анализа работы RS-триггера очевидно, что в том случае, если он находился в единичном состоянии Q=1, то для сброса его в нулевое состояние необходимо сигнал с прямого выхода Q подать на вход R сброса в нуль. Если же RS-триггер изначально находился в нулевом состоянии, т.е. и , то для приведения его в единичное состояние необходимо сигнал с выхода подать на вход S установки в единицу. Достигается это путем введения обратных связей ( рис. 5.9,а ). При этом, роль входа Т будет выполнять вход разрешения C синхронного RS-триггера.

Т-триггер можно построить и на базе D-триггера. Если в логическом уравнении синхронного D-триггера принять , тогда уравнение запишется в виде

Полученное выражение является ни чем иным, как логическим уравнением T-триггера при условии, что функцию входа T выполняет вход разрешения C D-триггера. При этом на вход D необходимо подавать сигнал с инверсного выхода ( рис. 5.9,б ).

Рис. 5.9. Синтез Т-триггера на базе синхронного RS-триггера и D-триггера.

Рассмотренные структуры Т-триггера являются практически нецелесообразными, поскольку характеризуются нестабильностью работы. Действительно, в течение всего времени, пока на входе T присутствует активный уровень сигнала, будет происходить непрерывная смена его состояний на противоположные с частотой, равной обратной величине времени задержки триггера. В результате возникает колебательный процесс. Причиной этого явления служит то, что Т-триггер, обладая обратными связями, принимает информацию как из внешней среды, так и со своих собственных выходов. Поэтому для устойчивой работы Т-триггера необходимо разделить во времени функции приема тактирующего сигнала Т и фиксации на входах R, S или D сигналов с соответствующих выходов Q и . Для этого в структуру Т-триггера вводится дополнительный второй запоминающий элемент на базе RS- или D-триггера. На синхронизирующий вход этого элемента тактовый сигнал подается в инверсном виде по отношению к тактовому сигналу первого запоминающего элемента. Подобная организация структур триггерных устройств называется двухступенчатой.

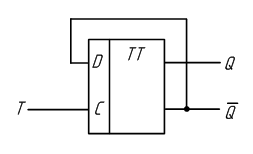

Пример двухступенчатого Т-триггера на базе двух синхронных RS-триггеров приведен на рис. 5.10,а , а на основе двух D-триггеров – на рис. 5.10,б . Из рисунка видно, что когда на синхронизирующем входе первого триггера в двухступенчатой структуре действует нулевой уровень тактирующего сигнала Т, он хранит свое состояние Q1 и . В это время на синхронизирующий вход второго триггера поступает инвертированный сигнал Т, т.е. имеющий уровень логической единицы. В результате второй триггер принимает состояние первого, т.е. Q1=Q2 и =. Запись в первый триггер при этом запрещена. Как только тактирующий сигнал Т примет уровень логической единицы, произойдет запись информации из второго триггера в первый. В результате состояние первого триггера изменится на противоположное. При этом запись во второй триггер производиться не будет, поскольку на его входе будет действовать нулевой уровень сигнала разрешения записи. Процесс будет повторяться с приходом каждого тактирующего импульса, что обеспечит устойчивую работу устройства. В условных графических обозначениях всех двухступенчатых триггеров принято в обозначении функции элемента указывать два символа «ТТ», как это показано на примере двухступенчатого Т-триггера ( рис. 5.10,в ). Вход Т Т-триггера принято называть счетным.

Рис. 5.10. Двухступенчатый T-триггер на базе синхронных RS-триггеров и D-триггеров и его условное графическое обозначение.

JK-триггер. JK-триггер относится к двухвходовым устройствам и функционирует по правилам, похожим на правила функционирования RS-триггера. Отличие состоит в том, что в JK-триггере все состояния являются определенными. Можно провести аналогию входов JK- и RS-триггеров: вход K JK-триггера выполняет функцию входа R RS-триггера, а вход J JK-триггера – функцию входа S RS-триггера. При этом, если в RS-триггере комбинация единичных значений входов R и S является запрещенной, то в случае аналогичной комбинации J— и K-входов, JK-триггер меняет свое состояние на противоположное. Правило работы асинхронного JK-триггера можно сформулировать следующей таблицей переходов: